2024年9月24日,周晔教授团队在自然指数期刊《Journal of Physical Chemistry Letters》发表了题为“Dual-Mode Reconfigurable Split-Gate Logic Transistor through Van der Waals Integration”的研究论文。该研究论文探讨了通过范德华集成实现双模式可重构分离栅逻辑晶体管。课题组博士后陈雪和三年级本科生薛昊哲为共同第一作者,周晔、李峰、郭霁庆为通讯作者,深圳大学为第一完成单位。

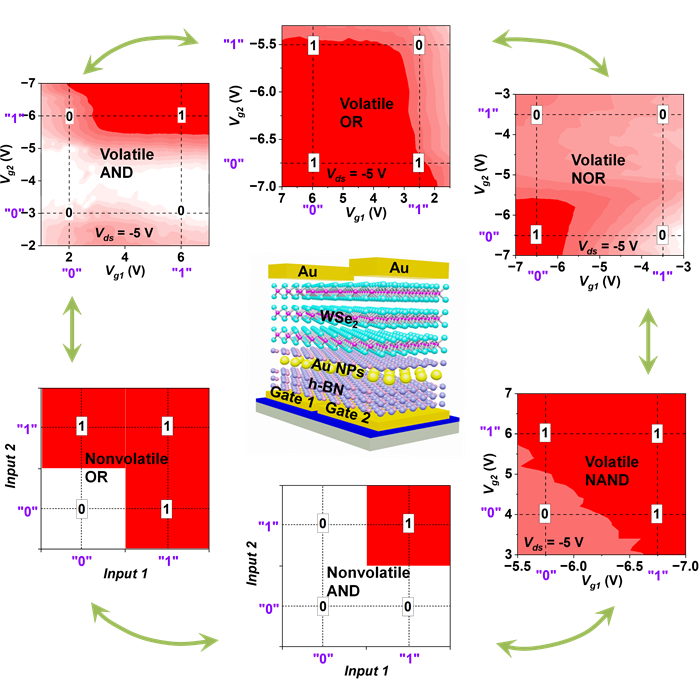

随着硅基晶体管接近其物理尺寸极限,基于二维材料的可重构功能电子器件被认为是超越摩尔策略的最有前途的新型器件架构。虽然这些器件受到了极大的关注,但它们通常需要复杂的器件制造工艺和额外的电场。此外,器件性能通常受到金属-半导体界面特性的限制。这项研究构建了一个基于WSe2晶体管的可重构逻辑器件,该晶体管具有纳米浮栅和通过范德华集成实现的分离栅极。该器件实现了较小的肖特基势垒,通过改变分离栅极的电压,只需一个器件即可实现易失性可重构同质结以及AND、OR、NOR和NAND逻辑操作。此外,借助纳米浮栅的电荷捕获效应,还可以实现非易失性可重构同质结,以及AND和OR逻辑操作。易失性和非易失性逻辑操作分别类似于人脑中突触的短期可塑性和长期可塑性。这项工作为构建具有简单制造工艺和低成本的新型可重构功能电子器件提供了一种潜在的方法。

此项研究得到国家自然科学基金、英国皇家化学会、射频异质异构集成全国重点实验室自主课题、广东省基础与应用基础研究基金、深圳市科创局、深圳大学与台北科技大学2024年合作研究项目的资助。

原文链接:https://pubs.acs.org/doi/10.1021/acs.jpclett.4c02397

撰稿:周晔 审核:刘俊芳、李晓光、李猛